Unlock the Full Potential of MAX 10 ADC Conversion Data with Post-Processing

Table of Contents

- Introduction

- Creating the ADC with External Storage Mode

- Creating the PLL

- Setting up the In-System Source and Probe

- Designing the Sequencer Control Block

- Configuring the External Sample Storage Control Block

- Post-Processing the ADC Data

- Implementing LED Threshold for Channel 7

- Conclusion

- Design Files

Introduction

🌟 How to Export ADC Conversion Data into the core for Post Processing 🌟

In this article, we will explore the process of exporting ADC conversion data into the core for post-processing. We will cover the step-by-step guide on creating an ADC with the standard sequencer and external storage mode. We will also delve into the creation of a PLL to drive the ADC Qsys clocking and operation. Additionally, we will discuss the implementation of a state machine to kick-start the ADC operation. Moreover, we will explore the process of registering the ADC conversion data into the core for post-processing and provide an example of post-processing techniques. So, let's dive in and discover how to unleash the full potential of ADC conversion data!

Creating the ADC with External Storage Mode

🔍 Step 1: Selecting the ADC Modular Core in Qsys

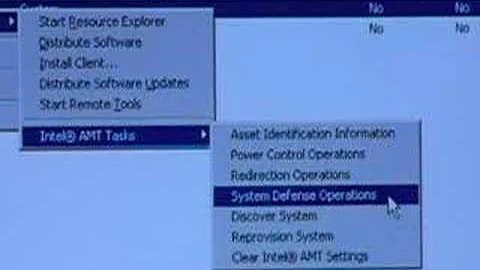

To begin the process, navigate to Qsys and select the Altera ADC modular core. In the Core Variant, choose the Standard Sequencer with External Storage mode. Ensure that the debug path is disabled for the first ADC. Select 10MHz as the ADC input clock, which can be changed to an external source if available.

Step 2: Configuring Channels and Sequencer

In the Channels tab, select the desired channel(s) for sampling. Enable all channels for sampling, including TSD (Temperature Sensor Diode). On the Sequencer tab, we have up to 64 slots available. For simplicity, we will create 10 slots, with one slot dedicated to each channel.

Step 3: Making Connections and Exporting Ports

Make the necessary connections within the ADC module. Export the required ports to enable proper communication with other components of the system. Generate HDL to proceed to the next step.

Creating the PLL

🔍 Step 1: Selecting the PLL Configuration

In this step, a PLL will be created to provide clock signals for the ADC operation. Set the refclk of the PLL to 50MHz, matching the external clock oscillator frequency. Generate a 10MHz clock signal for the ADC, as defined previously.

Step 2: Adding In-System Source and Probe

Navigate to the IP catalog and select "In-System Source and Probe" (ISSP). Provide a suitable name for the ISSP component. For this configuration, we won't be probing anything, so the probe number will be set to 0. Select the appropriate source for the ISSP.

Step 3: Adding Files to the Project

Add the ISSP configuration file to the project to integrate it into the system. At this point, we have successfully created the ADC with external storage mode, the PLL, and the ISSP using Altera's IP catalog and Qsys.

Designing the Sequencer Control Block

🔍 Step 1: Coding the Sequencer Block

The sequencer block is responsible for controlling the ADC operation. It waits for a "start trigger" signal from the ISSP and ensures that the reset is completed by waiting for a few cycles. Once the reset is completed, it writes to address offset 0x0 to run continuously.

Configuring the External Sample Storage Control Block

🔍 Step 1: Setting Up the Sample Storage Block

The external sample storage block involves creating a 12-bit register storage for each channel. Depending on the response validity, data, and channel, the ADC conversion data will be stored in the corresponding channel's register. For example, the ADC response value on channel 1, 55Ah, will be updated on ADC value 01.

Post-Processing the ADC Data

🔍 Step 1: Analyzing the ADC Data

At this stage, it is up to the user to decide how they would like to post-process the ADC data. Various techniques can be applied depending on the requirements and objectives. In this example, we will focus on post-processing Channel 7 data and displaying it on an LED when it exceeds a defined threshold.

Implementing LED Threshold for Channel 7

🔍 Step 1: Threshold-Based LED Display

To implement the LED threshold functionality, adjustments can be made to the analog input. As the analog input increases, more LEDs will turn on based on the defined threshold. The higher the analog input, the more LEDs will turn on, indicating the exceeding threshold levels.

Conclusion

🎉 Unleash the Full Potential of ADC Conversion Data 🎉

In conclusion, this article has provided a comprehensive step-by-step guide on exporting ADC conversion data into the core for post-processing. We have discussed the creation of an ADC with external storage mode, the configuration of a PLL, and the setup of the In-System Source and Probe. Additionally, we delved into the design of the sequencer control block and the external sample storage control block. We also explored post-processing techniques and implemented an LED threshold display for Channel 7 data. By following these steps, you can effectively utilize and enhance the capabilities of ADC conversion data.

Design Files

The design files used in this guide can be found at the following link on the Altera wiki: Design Files

FAQs

Q: Can I use an external clock source for the ADC?

A: Yes, you can change the ADC input clock to an external source if available.

Q: How many slots are available in the sequencer?

A: The sequencer allows for up to 64 slots, but for simplicity, we have created 10 slots in this example.

Q: How can I customize the post-processing of ADC data?

A: The post-processing techniques can be tailored to your specific needs and objectives. You have the flexibility to choose the most suitable methods for analyzing and utilizing the ADC data.

Q: Are there any additional resources available for further exploration of ADC post-processing techniques?

A: Yes, the Altera wiki provides additional resources and documentation on ADC post-processing techniques. You can refer to the provided links to access these resources.

WHY YOU SHOULD CHOOSE TOOLIFY

WHY YOU SHOULD CHOOSE TOOLIFY