Hướng dẫn tham số hóa bộ điều khiển DDR3 SDRAM của Altera

Mục lục

- Giới thiệu về việc parameterize bộ điều khiển DDR3 SDRAM

- Chuẩn bị phần cứng và phần mềm

- Tạo dự án và tìm thiết bị phù hợp

- Cài đặt các tham số cho bộ điều khiển DDR3 SDRAM

- Tốc độ giao diện bộ nhớ

- Tần số tham chiếu PLL

- Giao diện chia sẻ và tham số bộ nhớ

- Cài đặt bộ điều khiển chế độ (Mode Register)

- Thiết lập đặc tính định thời của bộ nhớ

- Điều chỉnh tín hiệu trên bo mạch

- Cấu hình giao diện Avalon và ánh xạ địa chỉ

- Cài đặt thanh kiểm tra lỗi và tùy chọn mô phỏng

- Tạo ra nguồn điều khiển DDR3 SDRAM dự án mẫu

- Sử dụng Altera Quartus Programmer để nạp chương trình vào vi xử lý

- Kiểm tra giao diện bộ nhớ ngoại vi

- Kết luận

Hướng dẫn tham số hóa bộ điều khiển DDR3 SDRAM của Altera

Xin chào, tôi là Gavin Loft, một kỹ sư ứng dụng tại Altera. Hôm nay, tôi sẽ hướng dẫn bạn cách tham số hóa bộ điều khiển DDR3 SDRAM của Altera và sau đó, chúng ta sẽ thực hiện mô phỏng bộ điều khiển này trên thiết bị phần cứng bằng việc sử dụng một mẫu thiết kế. Mẫu thiết kế này bao gồm một bộ tạo mẫu và bộ kiểm tra được sử dụng để thực hiện ghi và đọc từ bộ điều khiển và kiểm tra tính chính xác của dữ liệu. Dưới đây là thiết bị phần cứng mà chúng tôi sẽ sử dụng: Development Kit FPGA Stratix 5 và USB Blaster được kết nối với máy tính xách tay của tôi. Phần mềm Altera Quartus 13.1 sẽ được sử dụng để tạo IP, biên dịch dự án và cấu hình thiết bị.

Đầu tiên, chúng ta sẽ tạo dự án trong phần mềm Quartus. Sau đó, chúng ta chọn thiết bị mục tiêu cho dự án. Dựa trên số hiệu sản phẩm, tôi đã chọn thiết bị Stratix 5. Tiếp theo, tôi mở trình quản lý tiện ích mega wizard để tạo IP. Tôi sử dụng hộp tìm kiếm để tìm bộ điều khiển DDR3 SDRAM và sau đó đặt tên và tạo cấu hình biến thể mới của IP.

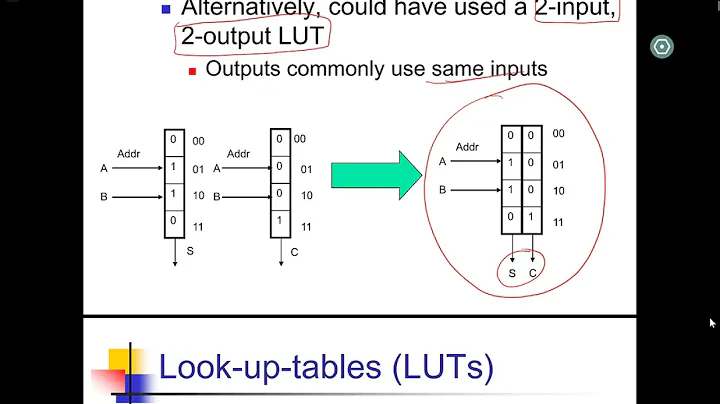

Tiếp theo, tôi nhập các thông số cần thiết cho bộ điều khiển. Tôi đã chọn tốc độ giao diện bộ nhớ dựa trên ước lượng của bộ ước lượng giao diện bộ nhớ ngoại vi và tốc độ grad của các thiết bị bộ nhớ được gắn trên bo mạch. Tôi cũng đã sử dụng bộ ước lượng tham chiếu để quyết định tần số tham chiếu PLL dựa trên những gì có sẵn trên bo phát triển.

Tiếp theo, tôi chọn các tham số của bộ nhớ mà tôi đang sử dụng: Micron và các thiết bị riêng lẻ được lắp trực tiếp lên bo mạch. Tốc độ 800 MHz, giao diện 72 bit và các coil địa chỉ được truyền từ nhóm dữ liệu G của thiết bị.

Trong phần cài đặt bộ điều khiển chế độ, tôi chọn các thiết lập cho bộ điều khiển chế độ trên bộ nhớ dựa trên các thông số kỹ thuật của thiết bị bộ nhớ và các thiết lập kết thúc được chọn dựa trên mô phỏng bo mạch.

Tiếp theo, trong tab thời gian của bộ nhớ, tôi nhập các tham số định thời cho thiết bị bộ nhớ mà tôi đang sử dụng. Trong cửa sổ presets, có một số thiết bị liệt kê và thiết bị Micron của tôi được bao gồm trong danh sách.

Trong tab cài đặt bo mạch, tôi nhập đặc điểm vật lý của các tín hiệu trên bo mạch và khoảng cách giữa các tín hiệu khác nhau từ thiết bị bộ nhớ. Đồng thời, tôi cũng nhập chỉ số đo giữa các thiết bị bộ nhớ và dụng cụ FPGA để đo đa vi bên cạnh FPGA chứ không phải Pin của FPGA.

Trong tab cài đặt bộ điều khiển, tôi có thể thiết lập giao diện Avalon và ánh xạ địa chỉ giữa giao diện Avalon và địa chỉ trên bộ nhớ. Cuối cùng, trong tab chẩn đoán, tôi kích hoạt bộ công cụ e-myth và thiết lập các tùy chọn mô phỏng.

Sau khi tôi nhấn nút hoàn thành, tôi được cung cấp tùy chọn để tạo mẫu thiết kế mẫu. Tôi để tùy chọn này được chọn và nhấn nút tạo.

Sau khi quá trình tạo ra bộ điều khiển DDR3 IP hoàn tất, tôi mở dự án mẫu đã được tạo ra. Bạn sẽ nhận thấy rằng dự án mẫu hiển thị thiết bị Stratix 5 không đúng, vì vậy tôi cần phải chọn thiết bị chính xác trên bo mạch.

Trước khi thêm bất kỳ chỉ định nào vào dự án này, tôi sẽ chạy phân tích và tổng hợp để tạo ra danh sách mạng, cho phép các tập lệnh chỉ định tự động được liên kết và tìm hiểu những gì được kết nối với bộ điều khiển DDR3 IP.

Tiếp theo, tôi sẽ chạy Pinnace với tập lệnh Tickles được tạo bởi DDR3 IP để áp dụng tất cả các ràng buộc I/O và nhóm DQ/DQS cần thiết cho IP.

Tôi cần phải thực hiện đặt vị trí chân riêng cho bo mạch này. Tôi sử dụng một tập lệnh mẫu để làm điều này, tuy nhiên, nếu bạn sử dụng một làm đồng nhất, bạn có thể sử dụng bộ lập kế hoạch chân.

Sau khi dự án của tôi có tất cả các ràng buộc thích hợp, tôi có thể bắt đầu quá trình biên dịch đầy đủ. Việc này có thể mất vài phút, vì vậy tôi sẽ đi ra khỏi và quay lại khi nó hoàn tất.

Sau khi quá trình biên dịch hoàn tất, tôi có thể tiến hành nạp chương trình cho bo mạch của mình bằng Altera Quartus Programmer. Trong hộp thiết lập phần cứng, tôi chọn thiết lập USB Blaster và sử dụng nút tự động nhận diện JTAG để phát hiện chuỗi JTAG trên bo mạch.

Sau đó, tôi gán tệp SOF mà tôi đã tạo ra trong quá trình biên dịch cho thiết bị mà tôi muốn cấu hình. Tôi chọn chế độ cấu hình từ bộ nhớ flash và sau đó bấm nút Bắt đầu.

Chương trình Quartus Programe báo cáo rằng thiết bị đã được cấu hình chính xác. Tôi sử dụng các đèn LED làm công cụ chẩn đoán trong dự án của mình, vì vậy hãy cùng nhìn vào phần cứng.

Sau khi FPGA đã được cấu hình, bạn có thể thấy rằng LED 0 và LED 1 đã được bật để chỉ ra lỗi cục bộ và trạng thái trình điều khiển không thành công.

Ngôn ngữ Verilog được sử dụng phổ biến trong thiết kế hệ thống kỹ thuật số và bộ điều khiển DDR3 SDRAM của Altera có thể được tùy chỉnh theo nhu cầu của bạn.

Bây giờ, tôi sẽ sử dụng bộ công cụ giao diện bộ nhớ ngoại vi để kiểm tra kết quả hiệu chuẩn và xem xét các tham số định thời của giao diện.

Để sử dụng bộ công cụ giao diện bộ nhớ ngoại vi, tôi cần sử dụng các kết nối khởi tạo để khởi tạo kết nối JTAG với bo mạch và sau đó sử dụng Liên kết dự án với thiết bị để tạo liên kết giữa tệp SOF và chuỗi JTAG đã được phát hiện.

Cuối cùng, tôi sử dụng Tạo kết nối giao diện bộ nhớ để tạo kết nối giữa thiết bị trên bo mạch và bộ công cụ giao diện bộ nhớ ngoại vi. Tôi đặt tên này một cách tùy ý và tôi đã chọn DDR3 ở đây.

Sau khi tạo kết nối giữa bộ công cụ giao diện bộ nhớ ngoại vi và giao diện bộ nhớ ngoại vi, tôi có thể chạy báo cáo về hiệu chuẩn và cũng có thể thực hiện các kiểm tra gỡ lỗi như chạy lại hiệu chuẩn và chạy lại hiệu chuẩn với một số dãy số hàng hoặc nhóm DQ nhất định.

Một nhiệm vụ khác mà tôi có thể thực hiện là tạo báo cáo về biên độ.

Sau khi tôi chạy tác vụ tạo báo cáo biên độ, tôi sẽ chạy tác vụ tạo báo cáo nhiều, sẽ tạo ra tất cả các báo cáo hiệu chuẩn và hiển thị chúng trong cửa sổ báo cáo ở góc trên bên trái màn hình. ở đây có rất nhiều thông tin hữu ích trong các báo cáo này. Tóm tắt cho chúng ta thấy màn hình giao diện đã qua kiểm tra là thông tin chính. Các báo cáo khác cho biết về biên độ thời gian mà hiệu chuẩn phát hiện được trong suốt và chúng cũng cho chúng ta biết về các thiết lập của chuỗi trì trệ mà thuật toán hiệu chuẩn đã tạo ra. Bạn có thể tìm hiểu định nghĩa của các chuỗi trì trệ này trong sổ tay thiết bị tương ứng. Trong trường hợp này, đó là sổ tay SPICE của Stratix 5.

Báo cáo biên độ cung cấp cho chúng ta biểu đồ biểu diễn cửa sổ dữ liệu đọc và cửa sổ dữ liệu ghi. Các khu vực màu xanh lá cây cho chúng ta thấy những khu vực mà việc đọc hoặc ghi đã thành công và các khu vực màu đỏ cho thấy nơi mà việc đọc hoặc ghi đã thất bại. Đánh ghi màu đen cho biết điểm mẫu đã được chọn bởi bộ tạo mẫu và bạn có thể thấy nó cố gắng chọn một giá trị nằm ở trung tâm.

Và đó là kết thúc của video này. Bạn có thể sử dụng các liên kết này để truy cập vào thêm thông tin về giao diện bộ nhớ từ trang web của Altera. Cảm ơn bạn.

< 5K

< 5K

31.09%

31.09%

3

3

7.3K

7.3K

47.36%

47.36%

16

16

134.6K

134.6K

63.43%

63.43%

10

10

< 5K

< 5K

13

13

10.6K

10.6K

13.52%

13.52%

14

14

24.9K

24.9K

16.55%

16.55%

66

66

< 5K

< 5K

25.2%

25.2%

10

10

45.7K

45.7K

16.2%

16.2%

45

45

6.3K

6.3K

29.81%

29.81%

3

3

WHY YOU SHOULD CHOOSE TOOLIFY

WHY YOU SHOULD CHOOSE TOOLIFY